Aktivita Programovatelný hardware je zaměřena na výzkum a vývoj specializovaných nástrojů pro monitorování a zabezpečení vysokorychlostních sítí, založených na programovatelném hardwaru, především hradlových polích – FPGA (více na www.cesnet.cz/projekt/02, www.liberouter.org).

Cílem aktivity Sledování a optimalizace výkonnostních charakteristik je výzkum a vývoj směřující k zajištění požadovaných výkonnostních charakteristik komunikace v rozlehlých vysokorychlostních sítích (více na www.cesnet.cz/projekt/07).

FPL byla první a dosud je největší mezinárodní akcí zaměřenou na prudce se rozvíjející oblast programovatelných logických obvodů a aplikací. Během posledních osmnácti let, kdy se konference pořádají, došlo v této oblasti k velkému pokroku, ať už jde o rekonfigurovatelnou architekturu, příslušné aplikace, navrhované metody a nástroje a podobně. Mnoho z těchto výsledků bylo poprvé prezentováno právě v rámci konferencí FPL.

Konference FPL se pořádají jednou za rok v Evropě za účasti předních kapacit oboru. Pražské setkání pořádal Ústav teorie informatiky a automatizace Akademie věd České republiky ve spolupráci se sdružením CESNET a univerzitami, které jsou aktivní v tomto oboru (Vysoké učení technické v Brně, ČVUT v Praze, Masarykova univerzita v Brně). Cílem setkání bylo svést dohromady výzkumné pracovníky z celého světa, aby diskutovali o problematice hradlových polí (FPGA), o odpovídajících aplikacích, pokročilé elektronické automatizaci navrhování (EDA), vestavěných procesorech, příslušné aritmetice, dynamické rekonfiguraci a podobně (více na http://fpl2009.org/).

Jedním z výsledků, které CESNET na konferenci prezentoval, je programovatelná platforma pro monitorování síťových linek o rychlosti 40 Gb/s. Zpracování bitového toku probíhá v poli FPGA. Standardně je k dispozici firmware pro testování bitové chybovosti – BERT (Bit Error Rate Test) – pomocí pseudonáhodného vzorku – PRBS (Pseudo-Random Bit Sequence). Podle potřeby lze vytvořit firmware pro jiný typ analýzy nebo generování provozu. Součástí platformy je výměnný optický transceiver standardu 300-pin MSA. To umožňuje připojení na linky s různými optickými modulacemi (např. NRZ, ODB, DPSK) i na linky s technologií OTN (Optical Transport Network) OTU-3, tedy v pásmu 43 Gb/s.

CESNET plánuje zařízení doplnit o analýzu a statistiky rámců OTN/SONET/SDH a o možnost dynamické rekonfigurace modulů pro zpracování síťového provozu, obdobně jako je tomu u platformy pro rychlost 10 Gb/s, která byla rovněž představena na konferenci FPL.

Sdružení na konferenci prezentovalo i další nové členy rodiny karet COMBOv2, určených pro vývoj a výzkum ve vysokorychlostních sítích. Návrh rodiny COMBOv2 umožňuje vyvinout karty rozhraní pro novou generaci Ethernetu s rychlosti 40Gb/s a 100Gb/s.

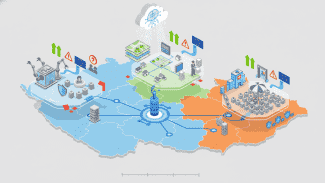

Sdružení CESNET bylo založeno vysokými školami a Akademií věd ČR. V současnosti je financováno především z prostředků vládní Rady pro výzkum a vývoj a z prostředků svých členů. Sdružení se zabývá výzkumem a vývojem informačních a komunikačních technologií, buduje a rozvíjí národní gigabitovou optickou síť CESNET2 určenou pro výzkum a vzdělávání. Díky výzkumným aktivitám a dosaženým výsledkům sdružení CESNET reprezentuje Českou republiku v projektu budování panevropské sítě GÉANT3 a podílí se aktivně na jeho realizaci. Více na www.cesnet.cz.